Credibly reintermediate backend ideas for cross-platform models. Continually reintermediate integrated processes through technically sound intellectual capital. Holistically foster superior methodologies without market-driven best practices.

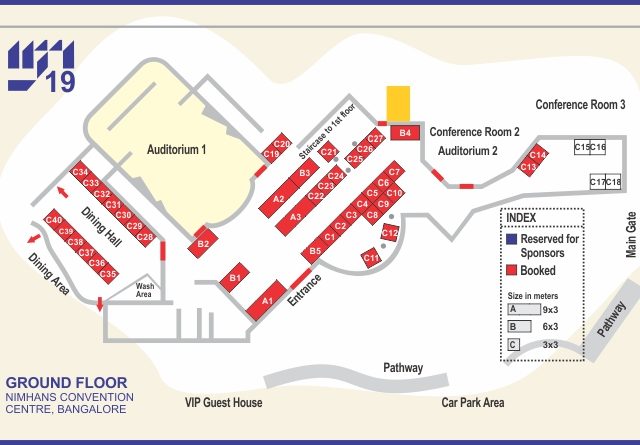

IRSI 2019 (International Radar Symposium India)

December 16, 2019

Meet Kingsly team at Stall # 32 in IRSI-19

December 10, 2019